## arm

Building Heterogeneous Chiplets with AMBA Interconnects

Jeff Defilippi, Senior Director Product Management Feb 26, 2023

© 2023 Arm

#### **Building Heterogeneous Chiplets with AMBA Interconnects**

- + The scalable AMBA CHI (Coherent Hub Interface) specification has provided the foundation for building complex SoCs across a broad range of applications including mobile, networking, automotive and data centers. The high-speed, credited, packetized attributes make it well suited to build multi-chip(let) networks.

- + This talk will highlight the scope of a new AMBA CHI Chip-to-Chip specification that is currently in development and illustrate how the specification will complement chiplet standards such as UCIe.

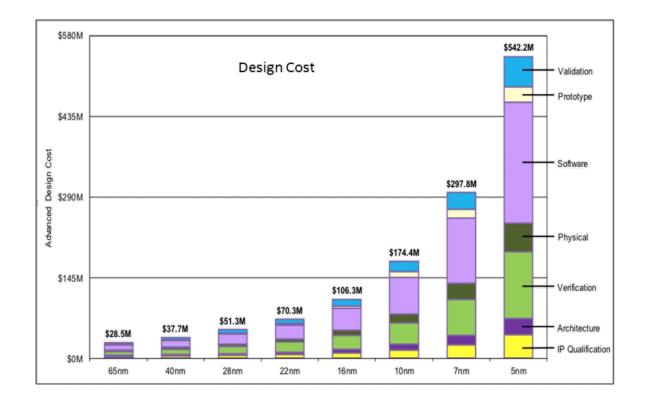

## **Economics Driving Chiplet Investments**

- --- Increasing design cost with less benefit

- Logic continues to scale, but IO & SRAM only shrinking by 5~10%

- + SoC NRE limiting product derivatives

- Chiplets lowers overall platform cost and barrier to deploy a diverse product portfolio

- Market demands performance and efficiency

- New chiplet technology offers a 20x speed and power improvement over traditional PCIe SERDES

Source: IBS, as cited in IEEE Heterogeneous Integration Roadmap

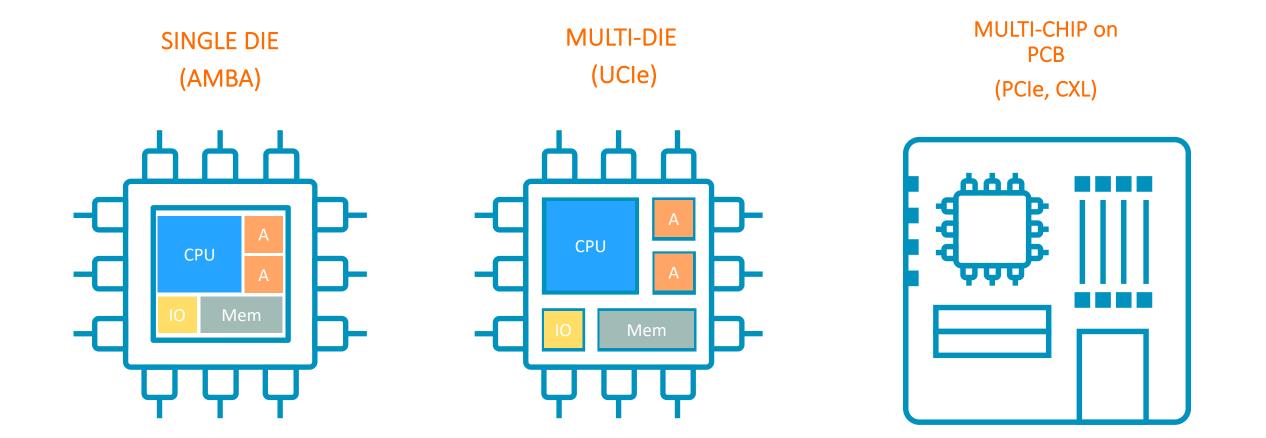

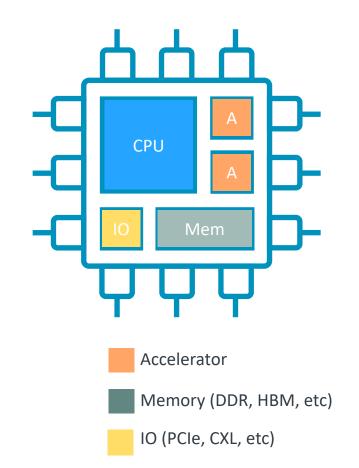

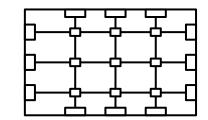

## SoC Accelerator Framework for Heterogenous Compute

Moving from Monolithic to Chiplet

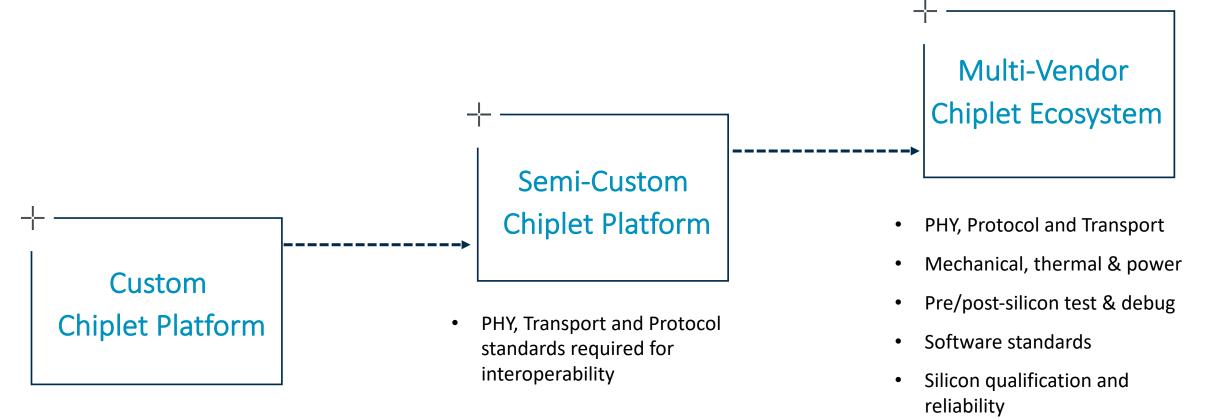

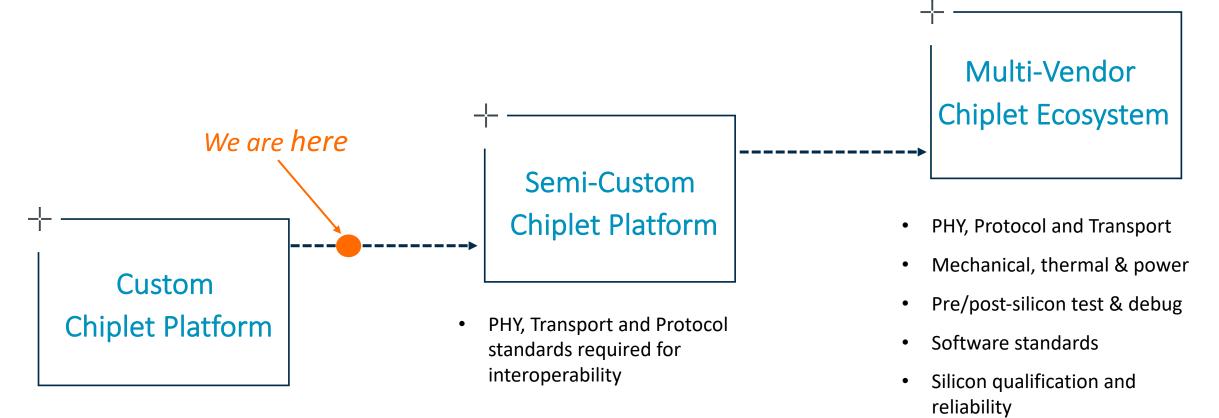

#### The Path to a Chiplet Ecosystem

PHY, Transport and Protocol standards drive IP development and broader adoption

arm

## The Path to a Chiplet Ecosystem

PHY, Transport and Protocol standards drive IP development and broader adoption

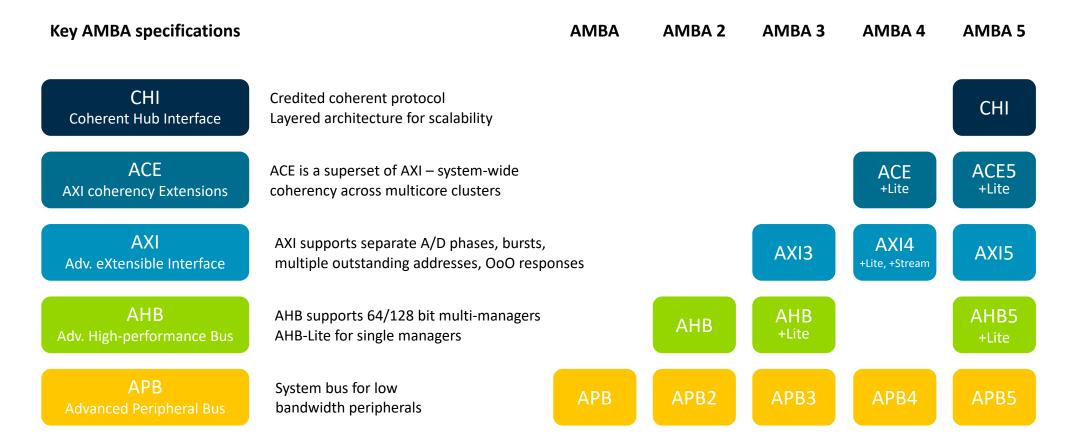

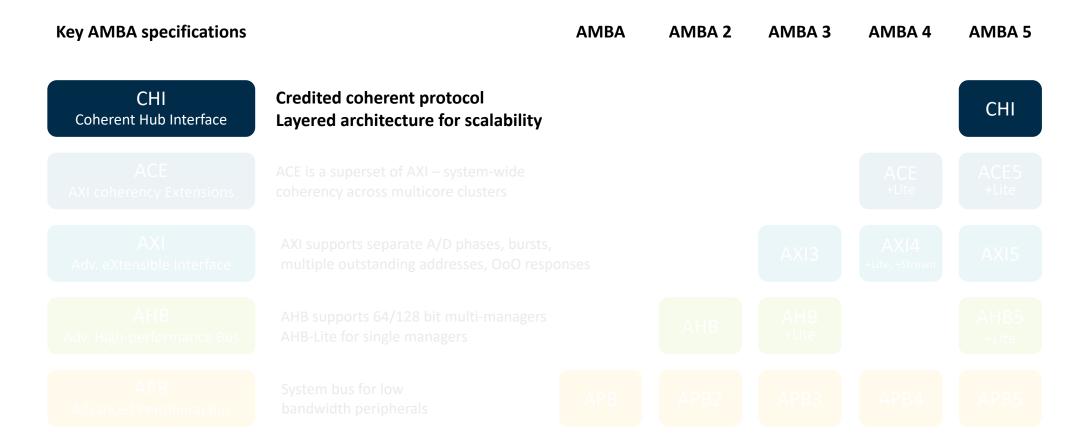

## AMBA: Specifications, Interface and Protocols Diagram

#### Key AMBA Specifications: CHI, ACE, AXI, AHB, APB

Selected AMBA specifications only. Other specifications include: ATB, ATP, CXS, DTI, GFB, LPI and LTI.

## AMBA: Specifications, Interface and Protocols Diagram

Key AMBA Specifications: CHI, ACE, AXI, AHB, APB

Selected AMBA specifications only. Other specifications include: ATB, ATP, CXS, DTI, GFB, LPI and LTI.

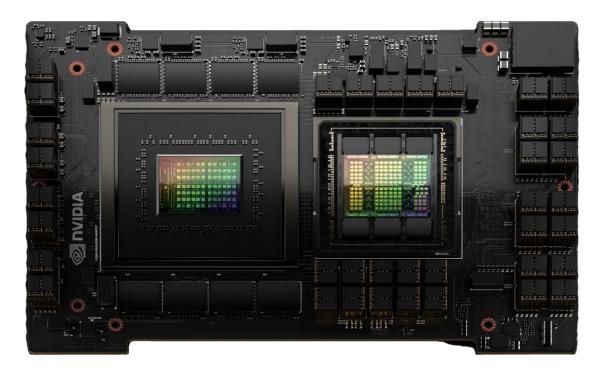

#### **NVIDIA Grace Hopper Superchip**

- Combining Grace CPU (72x Arm Neoverse V2 CPUs)

with Hopper GPU inside the package

- Hew 900 GB/s NVIDIA-CTC interconnect using AMBA CHI for the multichip protocol

- Unified virtual memory system with shared paged tables

- 30X Higher System Memory

B/W to GPU in a Server

#### Grace Hopper Superchip

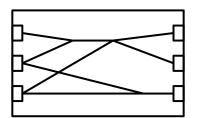

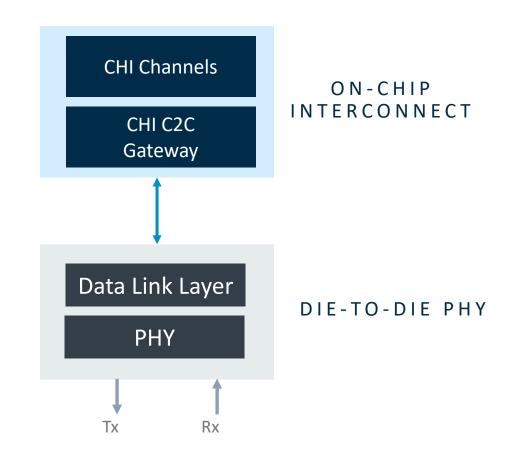

# Extending AMBA Architecture to Multichip with CHI C2C

- New AMBA CHI Chip-to-Chip Specification in Development

- + A unified interface for device attach

- Compute, Accelerator and Memory

- Coherent and IO Coherent accelerator traffic

- + Architectural features extended across chip(let) boundaries

- Virtualization (DVM), Interrupts, Timers

- Telemetry and Resource Management

- Security for trust, memory protection and Confidential Compute

- + Composable with die re-use across different solutions

- Appropriate for Multi-Die and Multi-chip through PCB

- Supports UCIe and bespoke PHY options

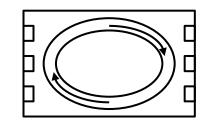

## **CHI Protocol Overview**

#### -- AMBA 5 CHI protocol features:

- Full cache coherency model

- Supports snoop filter and directory-based systems for snoop scaling

- Definition for simpler IO and Memory interfaces

#### - Other features:

- Credited, non-blocking, high-speed transports

- Configurable bus width 128, 256 or 512 bits

- Support for end-to-end *Quality of Service* (QoS)

- Virtual memory management through *Distributed* Virtual Memory (DVM) operations

#### Request Channel RSP Response Channel Data Channel SNP Snoop Channel

#### arm

#### AMBA CHI Specification:

https://developer.arm.com/search#q=amba%205%20chi%20architecture%20specification

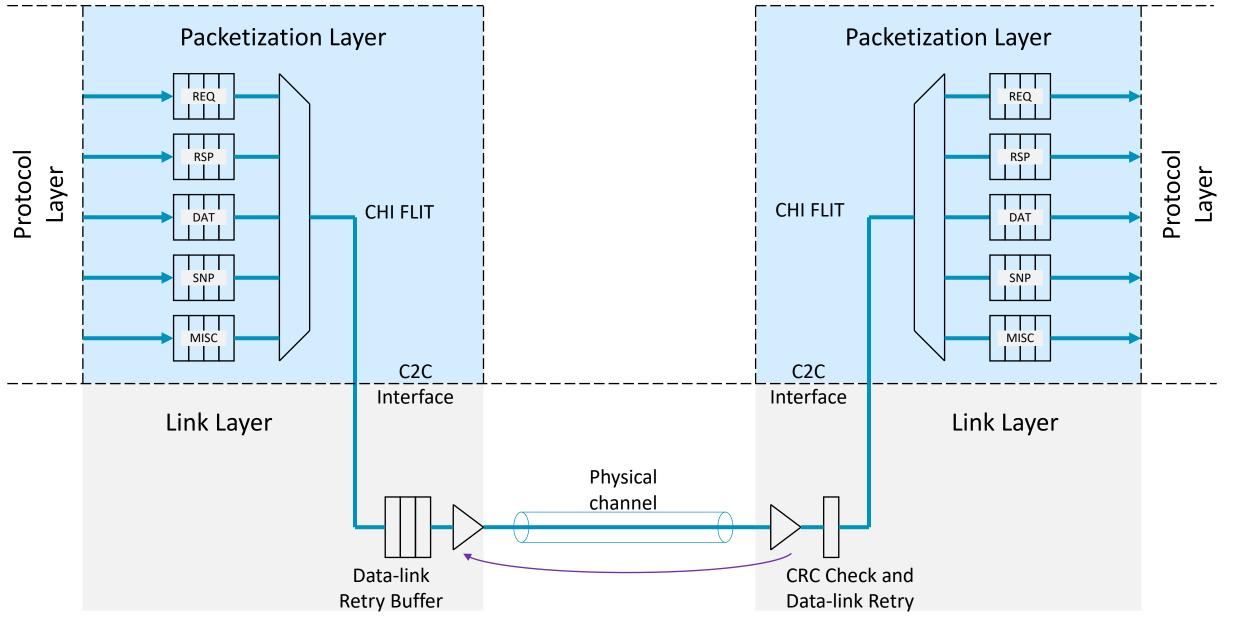

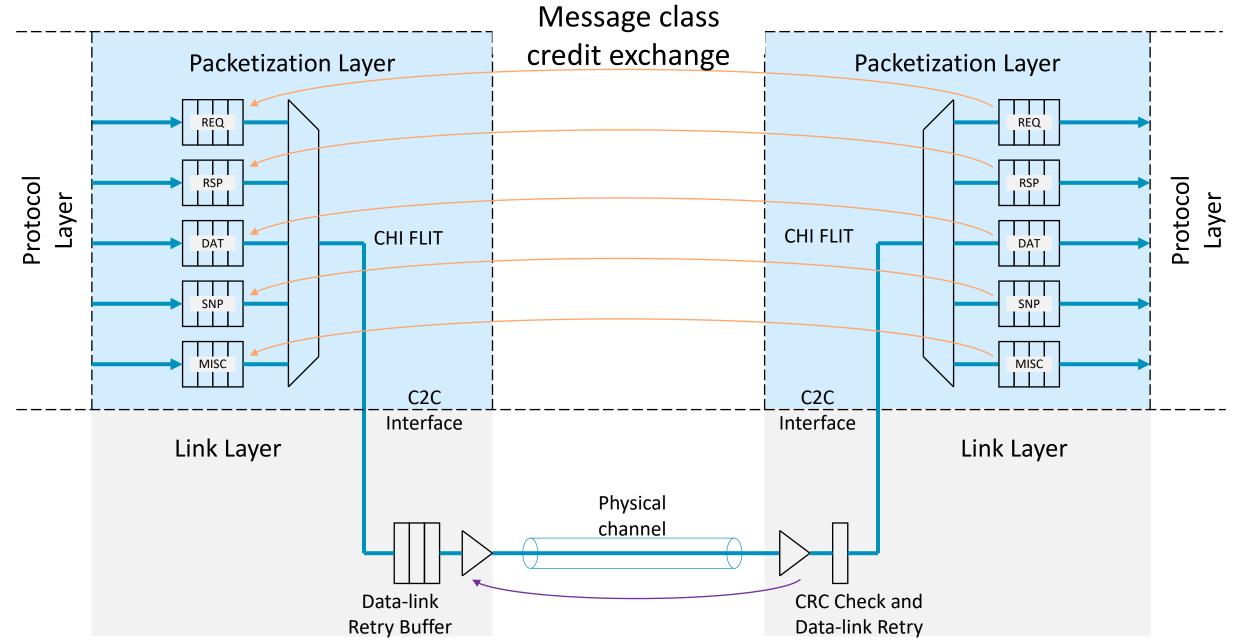

## **AMBA CHI Chip-to-Chip Specification**

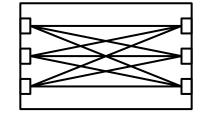

- + Packetization of CHI channels with cross-chip credit exchange

- + Link aggregation for bandwidth scalability

- + Portability across different PHY and packaging technology

- Clean interface definition between on-chip interconnect and PHY/Link Layer for IP portability between vendors

- + Support for point-to-point and chiplet network topologies

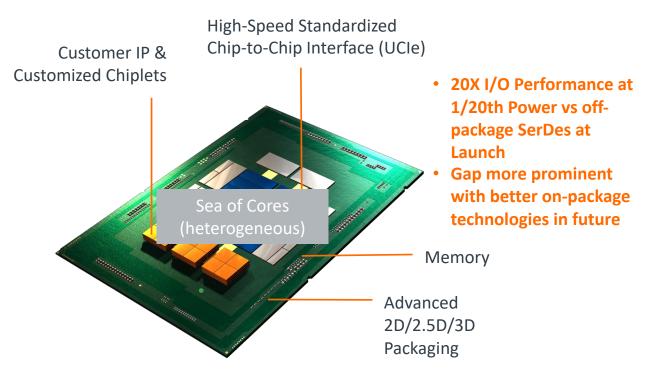

## **Open Chiplet: Platform on a Package**

Universal Chiplet Interconnect Express

Align Industry around an open platform to enable chiplet based solutions

- + Enables construction of SoCs that exceed maximum reticle size

- Package becomes new System-on-a-Chip (SoC) with same dies (Scale Up)

- + Reduces time-to-solution (e.g., enables die reuse)

- + Lowers portfolio cost (product & project)

- Enables optimal process technologies

- Smaller (better yield)

- Reduces IP porting costs

- Lowers product SKU cost

- + Enables a customizable, standard-based product for specific use cases (bespoke solutions)

- + Scales innovation (manufacturing and process locked IPs)

Heterogeneous Integration Fueled by an Open Chiplet Ecosystem (Mix-and-match chiplets from different process nodes / fabs / companies / assembly)

#### **UCle Layered Architecture**

- + UCIe 1.0 provides a complete multichip interface specification

- Leverages PCIe/CXL protocol for architectural agnostic attach

- PHY definitions for 2.1D and 2.5D packaging

- + AMBA CHI C2C will use the UCIe Streaming Interface

- Streaming interface with additional flit formats provide link robustness using UCIe defined data-link CRC and retry

- Arm will support both CHI and CXL/PCIe options to provide flexibility for the wide range of potential chiplet integrations

- + UCIe defines support for both 2.1D and 2.5D packaging

https://www.uciexpress.org/webinars

| PROTOCOL LAYER     | AMBA<br>CHI C2C                                                                                                                                                                              | CXL/PCIe |  |  |  |  |  |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|--|--|--|--|

| DIE-TO-DIE ADAPTER | ARB/MUX (when applicable)<br>CRC/RETRY (when applicable)<br>LINK STATE MANAGEMENT<br>PARAMETER NEGOTIATION                                                                                   |          |  |  |  |  |  |

| PHYSICAL LAYER     | LINK TRAINING<br>LANE REPAIR (when applicable)<br>LANE REVERSAL (when applicable)<br>SCRAMBLING/DE-SCRAMBLING (opt-in)<br>SIDEBAND TRAINING & TRANSFERS<br>ANALOG FRONT END<br>CLOCK FORWARD |          |  |  |  |  |  |

+

#### AMBA CHI C2C Extends on-chip performance to Multi-chip(lets)

- + Economics are driving chiplet investments and momentum toward Semi-Custom Chiplet Platforms

- Standards investments for PHY, Transport and Protocol IP accessibility and interoperability

- New PHY and packaging technology offering 'on-chip' performance and efficiency; 20x speed and power improvement over traditional PCIe SERDES

- + New AMBA CHI Chip-to-Chip specification will extend the on-chip bus to multi-chip

- Provides a unified memory, security and virtualization architecture across chiplets

- Built to run over standards based die-to-die interconnects such as UCIe or bespoke solutions

- Stay tuned!

- AMBA CHI C2C specification is under development, more updates expected throughout the year

|                    |  |  |  |  | × | ×          |  |

|--------------------|--|--|--|--|---|------------|--|

| Thank You          |  |  |  |  |   | ar         |  |

| × Danke<br>Gracias |  |  |  |  |   |            |  |

| × Grazie<br>谢谢     |  |  |  |  |   |            |  |

| ありがとう<br>Asante    |  |  |  |  |   |            |  |

| · Merci<br>감사합니다   |  |  |  |  |   |            |  |

| धन्यवाद<br>Kiitos  |  |  |  |  |   |            |  |

| شکرًا<br>ধন্যবাদ   |  |  |  |  |   |            |  |

| תוִדה <sub>×</sub> |  |  |  |  |   | © 2023 Arm |  |

arm

The Arm trademarks featured in this presentation are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved. All other marks featured may be trademarks of their respective owners.

www.arm.com/company/policies/trademarks

| © 2023 Arm |  |  |  |  |  |  |

|------------|--|--|--|--|--|--|

|            |  |  |  |  |  |  |

|            |  |  |  |  |  |  |

|            |  |  |  |  |  |  |

|            |  |  |  |  |  |  |

|            |  |  |  |  |  |  |